# **Topographic Electrical Characterization of Semi-Insulating GaAs, InP and SiC Substrates**

## R Stibal, S Müller and W Jantz

Fraunhofer Institut Angewandte Festkörperphysik, Tullastr. 72, D79108 Freiburg

Contactless mapping of the resistivity and contactless evaluation of the electron mobility of semi-insulating compound semiconductor substrates is achieved with the time-dependent capacitive measurement technique. High resolution images of state-of-the-art and exploratory substrates are presented, showing the absolute value and lateral variation of the resistivity in the range  $10^5$  to  $10^{12} \Omega$ cm. The topograms exhibit characteristic macro- and mesoscopic variation patterns related to the growth procedure as well as structural inhomogeneities and defect concentration variations. Very satisfactory agreement between conventional Hall data and mobility data measured with the innovative technique is obtained.

#### 1. Introduction

For high speed microelectronic applications semi-insulating (SI) wafers are advantageous to avoid the capacitive and inductive loading of a conductive substrate. For silicon based device technology costly approaches such as SOI or SIMOX are needed and intensively developed. By contrast, SI GaAs, InP and SiC is conveniently realized by incorporating, during the crystal growth, a deep donor or acceptor (EL2 in GaAs, Fe in InP, V in SiC) which provides complete ionization of shallow donors or acceptors. This compensation process and the resulting resistivity  $\rho$  depend on dopant and defect concentration distributions. Therefore, a detailed electrical characterization is needed for the production control of standard wafers and the analysis of exploratory material. In order to achieve and assess a specified, spatially homogeneous  $\rho$  value, topographic characterization is desired, which preferably should be nondestructive to avoid sacrificing expensive material. Recording small  $\rho$  variations with high lateral resolution across a large wafer area within acceptable time requires a highly repeatable and rapid measurement.

The contactless resistivity mapping technique meets these stringent demands very satisfactorily. We briefly summarize the basic approach and the performance of a system designed for routine industrial application. By repeating the  $\rho$  measurement with and without a magnetic field, the electron mobility  $\mu$  is obtained using the magnetoconductance effect. Hence, *complete* evaluation of the electrical transport properties of SI semiconductors is achieved with a noncontacting technique and without wafer cutting. Of course these advantages are particularly worthwhile for expensive material (SiC, InP) and for large size wafers (150 mm diameter GaAs). Typical resistivity topograms are presented. Contactless mobility data are summarized and compared with standard Hall and calculated results.

#### 2. Experimental details

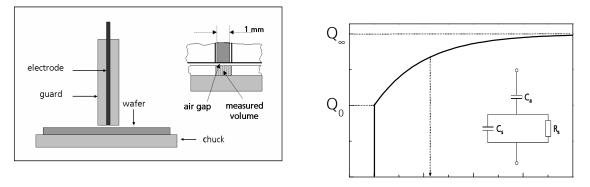

The contactless resistivity mapping procedure [1,2] evaluates the exponential decline, caused by the mobile carriers in the wafer material, of a voltage-induced dielectric polarization. As is shown in Fig.1, left side, the capacitive probe consists of a cylindrical metal stub, surrounded by a guard electrode. The metal chuck provides electrical back contact and mechanical support of the wafer to be measured. The stub is approached to the wafer surface (see insert), forming an air gap of about 50  $\mu$ m. A precise horizontal xy stage serves to translate the wafer underneath the probe in order to generate a  $\rho$  topogram. The equivalent circuit of the arrangement (insert in the right part of Fig.1) consists of the air capacitor of the shunt resistor representing the finite  $\rho$  of the wafer material.

The exponential time dependence of the charge Q(t) shown in Fig.1, right part, allows to measure the relaxation constant  $\tau$  and the charges Q(0),  $Q(\infty)$ . Together with the dielectric constant  $\varepsilon$  one obtains

$$\rho = \tau Q(0) / \varepsilon_0 \varepsilon Q(\infty) \tag{1}$$

Fig. 1 Left: Schematic representation of the COREMA measurement system. Righ? Charge transient observed after application of a voltage step. The quantities needed to calculate  $\rho$  with eq. (1) are indicated. The insert shows the equivalent circuit of the capacitive probe. The transient time depends on the resistivity and is about 10 µs for  $\rho = 10^7 \Omega$ cm.

The capacitive evaluation is fast (100 ms for  $\rho = 10^7 \Omega \text{cm}$ ), highly repeatable (better than 1 %) and yields topographic  $\rho$  images with high lateral resolution ( $\leq 1 \text{mm}$ ). For these reasons, the contactless resistivity mapping is superior to conventional contacting techniques, e.g. van der Pauw or linear four point probing. The measurement range is  $10^5 - 10^{12} \Omega \text{cm}$ .

The contactless measurement of  $\mu$  exploits the magnetoconductance effect. The time constants  $\tau(0)$  and  $\tau(B)$  measured with and without a magnetic field B yield

$$\mu = \mathbf{B}^{-1} \left( \left[ \tau(\mathbf{B}) / \tau(0) \right] - 1 \right) \frac{1}{2}$$

<sup>(2)</sup>

A horizontal magnetic field B = 0.8 Tesla is generated in the wafer plane within the measured sample volume with an appropriate arrangement of NdFe permanent magnets. Rapid consecutive measurements with and without B are conveniently enabled by mechanical displacement of the magnets. The method is applicable for  $\mu > 1000 \text{ cm}^2/\text{Vs}$  [3].

## 3. Resistivity topography

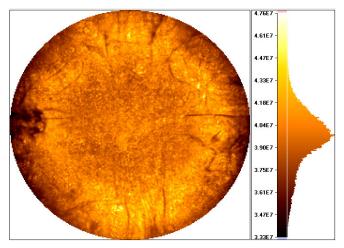

Fig. 2 shows the  $\rho$  topogram of a 150 mm GaAs wafer cut from a LEC grown ingot. It is very homogeneous, with a mean value  $3.97 \times 10^7 \ \Omega$ cm and a standard deviation of 4.3 % only. The measurement precision nevertheless allows to discern a number of significant fluctuation patterns. Macroscopic radial variations, cellular structure, streamers and a group of small cloudy areas of reduced resistivity at the left margin are clearly reproduced.

Fig. 2. Resistivity topogram and histogram of a semi-insulating 150 mm Ø LEC grown GaAs wafer.

The topographic resistivity evaluation is particularly helpful for SI SiC wafers, because this material is still in the development stage towards decreasing the concentration of shallow donors and controlling the incorporation of vanadium or other deep centers, such that exploratory material may exhibit strong  $\rho$  variations within very small distances.

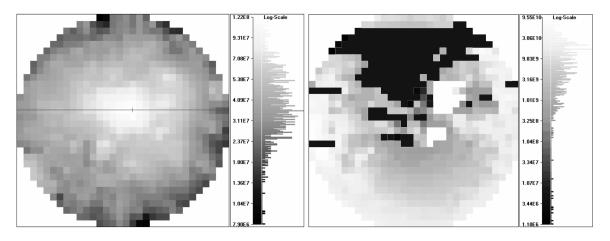

Fig. 3, left part, shows a homogeneous state-of-the art wafer which is entirely SI [4]. It has a mean  $\rho$  value of 3x 10<sup>7</sup>  $\Omega$ cm and a radial variation with a maximum in the center of the wafer. The wafer shown on the right side is in the 10<sup>10</sup>  $\Omega$ cm range, with two small areas (indicated white) even above the upper limit of the measurement range. However, a significant triangular portion of the wafer (indicated black) is below range (< 10<sup>5</sup>  $\Omega$ cm). This example clearly shows that single point measurements may be incomplete or misleading.

Fig. 3 Resistivity topograms of 2 inch SI SiC wafers [4]. The wafer on the left side is entirely SI in the  $10^7 \Omega$ cm range. The wafer shown on the right side is SI in the  $10^{10} \Omega$ cm range, but a portion (black triangular area) is below  $10^5 \Omega$ cm.

### 4. Contactless mobility measurement

The innovative contactless determination of the electron mobility  $\mu$ , developed to replace the destructive and time-consuming Hall procedure *entirely* for SI material, has been tested with a set of pre-characterized GaAs samples [3]. Very satisfactory agreement has been achieved using a laboratory system with a conventional electromagnet, but equivalent data have now also been obtained with the compact, user-friendly permanent magnet system described above. The agreement with data calculated using ionized impurity scattering theory and measured carbon concentrations values is excellent. These results show that the capacitive measurement may indeed will serve as a convenient, cost-saving and rapid alternative to the conventional Hall technique.

#### References

- [1] Stibal R, Windscheif J and Jantz W 1991 Semicond. Sci. Technol. 6 995-12001.

- [2] Stibal R, Wickert M, Hiesinger P and Jantz W 1999 Mat. Science Eng. B66 21-25.

- [3] Stibal R, Kretzer U and Jantz W 2002 GaAs MANTECH Digest of Papers, 75-78.

- [4] Stibal R, Müller S, Jantz W, Pozina G, Magnusson B, Ellison A, Proc. EXMATEC 2002, Budapest, to be published in phys. stat sol.